东京--(美国商业资讯)--东芝公司(TOKYO:6502)通过开发时域神经网络1 (TDNN),继续履行其促进物联网和大数据分析的承诺,TDNN利用极低功耗神经形态半导体电路处理深入学习。TDNN由大量微小处理单元组成,与传统的数字处理器不同的是,它采用东芝的原创模拟技术。TDNN是于11月8日在日本举办的2016年亚洲固态电路会议(A-SSCC 2016)上对外报道的,A-SSCC是由电气和电子工程师协会(IEEE)主办的国际半导体电路技术会议。

这份智能新闻稿包含多媒体内容。完整新闻稿可从以下网址查阅:http://www.businesswire.com/news/home/20161107005586/en/

深入学习需要大量的计算,这些计算通常在消耗大量功率的高性能处理器上进行。但是,将深入学习的功率传给传感器和智能手机等物联网边缘设备,需要高度节能的集成电路(IC),而这些集成电路可执行大量必要操作,同时仅消耗极低的能源。

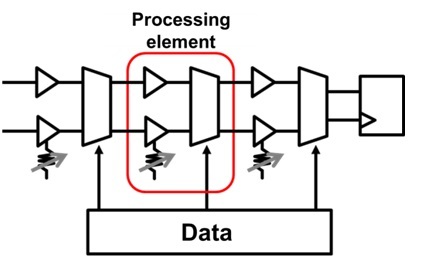

在冯·诺依曼(von Neumann)型2计算机体系结构中,多数能源是在将数据从芯片上或芯片外内存设备传输至处理单元时所消耗。减少基准移动的最高效方式是配置大量处理单元,而每个单元均专用于处理位于附近的唯一基准。这些基准点在输入信号(例如,一只猫的图像)转换为输出信号(例如猫图像识别)过程中被赋予权重。基准点离期望的输出越近,所赋予的权重越高。该权重提供用于自动指导深入学习处理的参数。

大脑具有类似的体系结构,因为神经元(权重数据)之间的耦合强度内置于神经键(处理单元)中。在这种情况下,神经键即是神经元之间的连接,而且每个神经键均具有不同的强度。该强度(权重)决定通过连接的信号。神经键用这种方式执行一种处理方式。这种可称为完全空间展开结构的体系结构颇为引人注目,但是它也存在明显的缺点——在芯片上复制需要大量能够快速变大的运算电路。

东芝的TDNN采用2013年开发的时域模拟与数字混合信号处理(TDAMS3)技术,可实现处理单元微型化。在TDAMS中,加法等运算操作通过将穿过逻辑门的数字信号延时作为模拟信号来高效执行。利用这种技术,深入学习处理单元可以只包含三个逻辑门及采用完全空间展开结构的1位存储器。东芝已制造出概念应证芯片,这种芯片将静态随机存取存储器(SRAM)单元作为存储器,并且可识别手写数字。每次操作的能耗为20.6 fJ4,比之前在某重要会议上报告的低六分之一5。

东芝计划将TDNN作为电阻式随机存取存储器(ReRAM)开发,以进一步提高能效和面积效率。其目标是集成电路可在边缘设备上实现高性能深入学习技术。

- TDNN:采用时域模拟与数字混合信号处理技术的神经网络

- 冯·诺依曼型:应用最广泛的标准计算机体系结构。该体系结构可将存储设备的数据加载到用于处理的处理单元上。

- TDAMS:一种模拟信号处理技术,将穿过逻辑门的数字信号延时作为模拟信号。由东芝开发。(参考:http://www.toshiba.co.jp/about/press/2013_02/pr2101.htm)

- 20.6fJ:相当于每秒进行48.6万亿次操作性能,功耗为1 W。

- 2016年国际固态电路会议(ISSCC 2016)论文编号24.2

关于东芝公司

东芝公司是一家《财富》全球500强公司,致力于将其在先进电子和电气产品及系统方面的一流能力运用于三大重点业务领域:更为清洁和安全的维持日常生活的能源业务;保持生活质量的基础设施业务;以及实现先进的信息社会的存储业务。在东芝集团的基本承诺“为了人类和地球的明天”的指引下,东芝竭力推动全球业务,并致力于实现一个让子孙后代可以享有更加美好的生活的世界。

东芝于1875年在东京成立,如今已成为一家有着550家附属公司的环球企业,全球拥有超过188,000名员工,年销售额逾5.6万亿日元(500亿美元)。(截至2016年3月31日。)

有关东芝的更多信息,请访问www.toshiba.co.jp/index.htm

原文版本可在businesswire.com上查阅:http://www.businesswire.com/news/home/20161107005586/en/

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

联系方式:

东芝公司

存储与电子元器件解决方案公司

Koichi Tanaka / Kota Yamaji

公共关系与投资者关系集团

业务规划部

电话:+81-3-3457-3576

semicon-NR-mailbox@ml.toshiba.co.jp

时域神经网络(图示:美国商业资讯)