东京--(美国商业资讯)--存储器解决方案全球领导者东芝存储器株式会社(Toshiba Memory Corporation)今日宣布成功开发出一种可实现高速、高容量固态硬盘的桥接芯片。东芝利用所开发的占用面积小、低功耗的桥接芯片,成功通过比无桥接芯片的传统方法更少的高速信号线连接更多的闪存芯片。公司于2月20日在旧金山2019国际固态电路会议(ISSCC 2019)上宣布了这一成果。

此新闻稿包含多媒体内容。完整新闻稿可在以下网址查阅:https://www.businesswire.com/news/home/20190221005378/en/

在固态硬盘中,多个闪存芯片与管理其运行的控制器相连。一旦与控制器接口相连的闪存芯片数量增加,其操作速度降低,因此限制了可连接的芯片的数量。为了提高容量,则需要增加接口数量,但这会造成需将大量的高速信号线连接到控制器上,因此增加了实现在固态硬盘板上进行布线的难度。

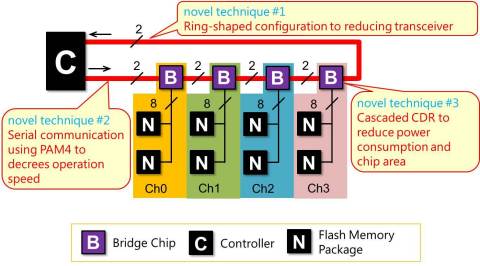

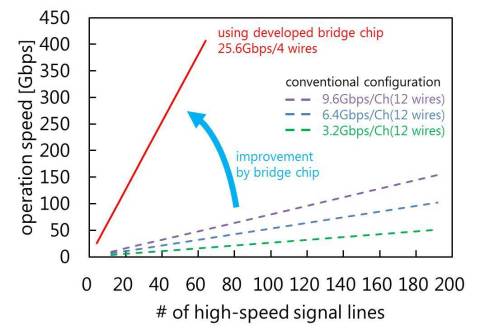

东芝利用所开发的可连接控制器与闪存芯片(图1)的桥接芯片解决了这一难题,并成功实现了三项创新技术:菊花链连接技术*1,以环形方式连接控制器和多个桥接芯片;使用PAM 4*2进行串行通信;以及抖动*3改进技术,可无需在桥接芯片中使用PLL电路*4。采用这些技术,能够降低桥接芯片的开销,并且仅通过几条高速信号线(图2)便能高速运行大量的闪存芯片。

桥接芯片和控制器的环形结构将桥接芯片所需的收发器数量从两对减少到一对,缩小了桥接芯片的面积。此外,在控制器与菊花链式桥接芯片之间采用PAM 4串行通信,可降低桥接芯片电路的运行速度,缓解它们所需承受的性能压力。新CDR*5利用PAM 4的特点改进抖动性,因此无需在桥接芯片中使用PLL电路,同时有助于缩小芯片面积、降低功耗。

桥接芯片原型采用28nm CMOS工艺制造,按照环形菊花链形式将四个桥接芯片与控制器连接对其性能进行了评估。该评估证实了所有桥接芯片和控制器在25.6 Gbps的速度下均能实现良好的PAM 4通信性能,而且也能够实现BER*6低于10-12。

接下来,东芝会进一步提升桥接芯片性能、缩小芯片面积和降低功耗,继续致力于开发工作,以实现前所未见的高速、大容量存储能力。

注

*1 菊花链:一种将多个芯片按顺序连接在一起的连接方式

*2 PAM 4:4电平脉冲幅度调制(包含4数值数据)

*3 抖动:时钟或信号波形时域的波动

*4 PLL:锁相环路(生成精确基准信号的电路)

*5 CDR:时钟数据恢复(从已接收的信号中恢复数据和时钟的电路)

*6 BER:位出错率(值越低,性能越高)

关于东芝存储器株式会社

作为存储器解决方案全球领导者,东芝存储器株式会社致力于闪存和SSD的开发、生产和销售。2018年6月,东芝存储器株式会社被一家由Bain Capital领衔的行业财团收购。东芝存储器株式会社开创性地开发出了一系列尖端的存储器解决方案和服务,丰富了人们的生活并扩大了社会的视野。该公司创新的3D闪存技术BiCS FLASH™将对先进智能手机、PC、SSD、汽车和数据中心等高密度应用领域存储器的未来产生深远影响。有关东芝存储器株式会社的更多详情,请访问:https://business.toshiba-memory.com/en-apac/top.html

原文版本可在businesswire.com上查阅:https://www.businesswire.com/news/home/20190221005378/en/

免责声明:本公告之原文版本乃官方授权版本。译文仅供方便了解之用,烦请参照原文,原文版本乃唯一具法律效力之版本。

联系方式:

东芝存储器株式会社

Kota Yamaji

商业规划部

电话:+81-3-6478-2319

semicon-NR-mailbox@ml.toshiba.co.jp

图1 使用桥接芯片连接(图示:美国商业资讯)

图2 桥接芯片带来的改进(图示:美国商业资讯)